Detailed Description This module contains all code and information on the preprocessor and how it works / is implemented The preprocessor is implemented mostly as part of the lexer, with the various compiler directives handled within the verilog_preprocessor_context structure and it's associated functions Function DocumentationVppreproc reads the Verilog files passed on the command line and outputs preprocessed output to standard out or the filename passed with o Note vppreproc was named vppp until release 3100, so if you're looking for vppp, this is the right replacement The vppp name conflicted with another nonVerilog related toolThe closest tool I'm aware of is the "if

Tree Sitter Verilog Module V At Master Tree Sitter Tree Sitter Verilog Github

System verilog ifdef or

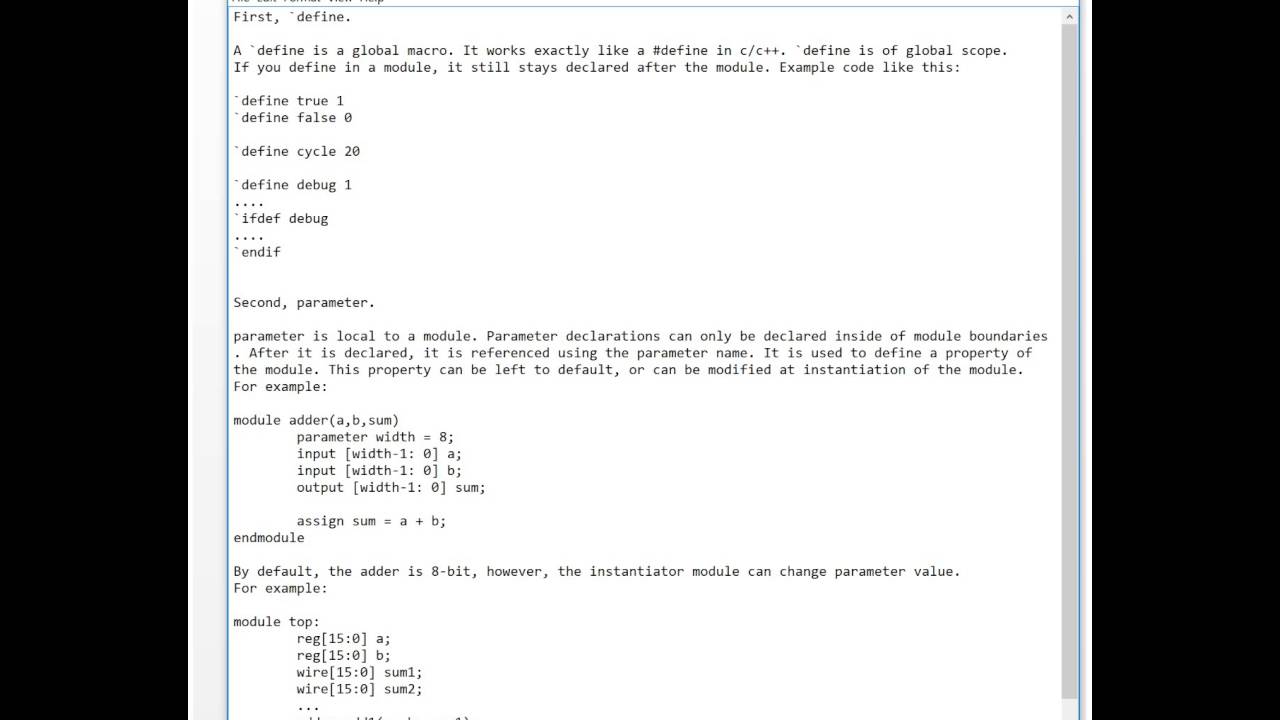

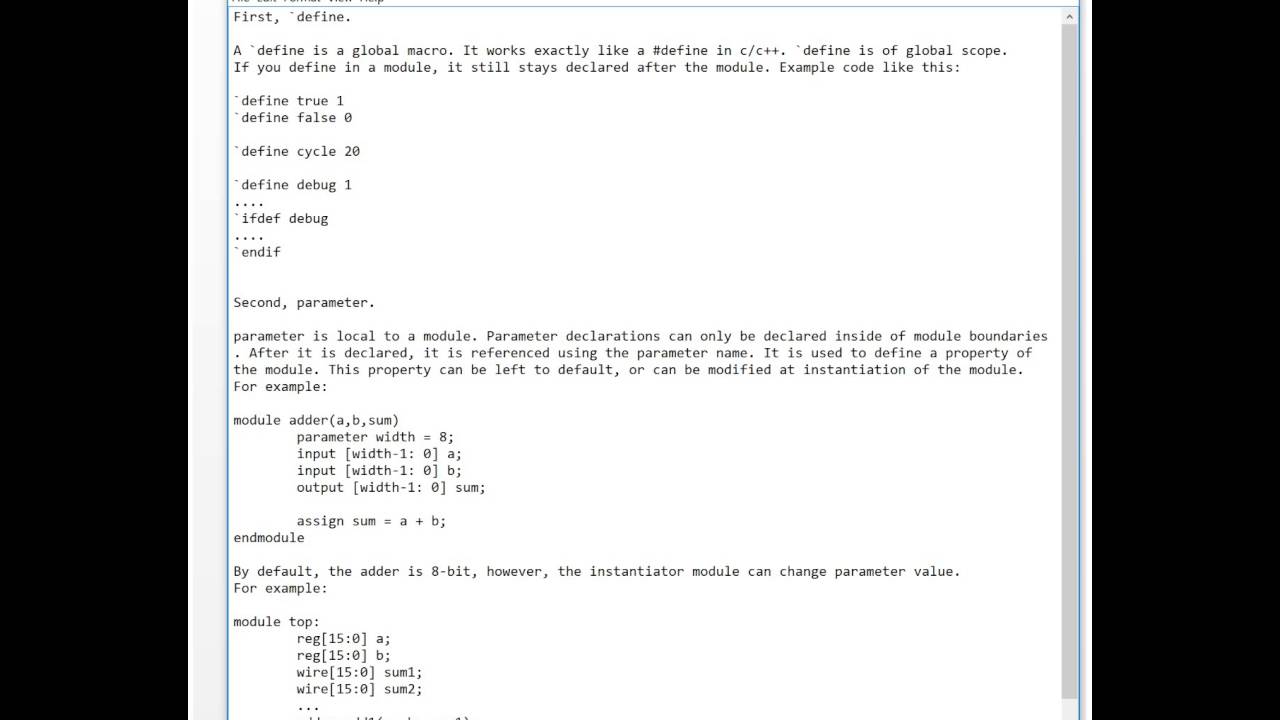

System verilog ifdef or- Verilog experts, but merit review As was just noted, the Verilog preprocessor is very similar to the C preprocessor, and many Verilog techniques directly correspond to C best practices Precedence The precedence problem occurs when a define is hastily created as follows `define OR(x,y) xyIt looks like the person who created your Verilog example was using the C preprocessor to handle his defines and macros Your example shows #ifdef which will work for C The Verilog preprocessor uses the "accentgrave" character or backwardssinglequote ` It is in the far upperleft of my keyboard Try this `ifdef TRIAL c(in3), `else c(in4

Verilog Tutorial 13 Define Parameter And Localparam Youtube

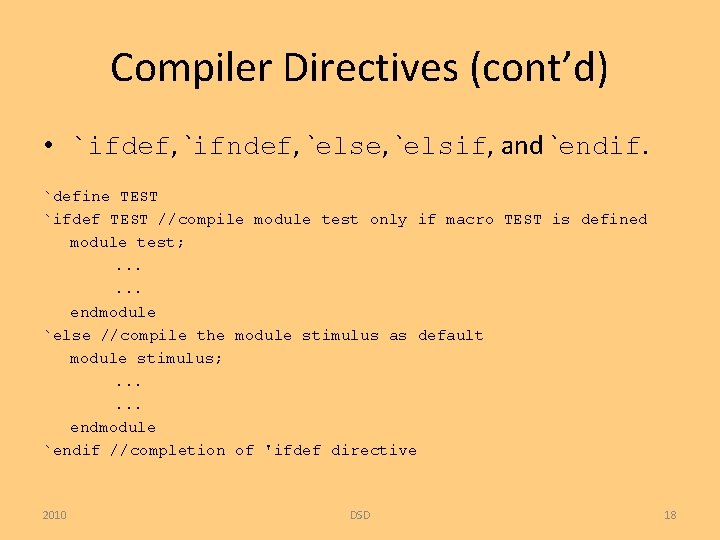

Different directives available in Verilog are `define `include `ifdef `ifndef `elseif `else `timescale `undef `resetall `defaultnettype;Negative numbers are represented as 2's compliment numbers !!!!! The Verification Community is eager to answer your UVM, SystemVerilog and Coverage related questions We encourage you to take an active role in the Forums by answering and commenting to any questions that you are able to

In Verilog, you can easily use the #ifdef preprocessor In VHDL, which is my first language, I can't replace it, specifically in this circumstance, with the generate statement which can't generate the parameters needed for the ports before starting anything in the block`ifdef FLASH_IS_1MB `define FLASH_TEA //19s max for 1MB erase cycle `elsif FLASH_IS_512KB `define FLASH_TEA //12s max for 512KB erase cycle `elsif FLASH_IS_256KB `define FLASH_TEA //6s max for 256KB erase cycle `elsif FLASH_IS_128KB `define FLASH_TEA //4s max for 128KB erase cycle `endif Some Verilog designs use a `define statement, possibly located inside a file referenced by an `include statement, to control something managed with `ifdef or `ifndef Instead of using a `define statement, you can define the Verilog macro with a Quartus setting in the qsf file You can control the v

GNU Emacs (VerilogMode)) module m (`ifdef c_input c, `endif /*AUTOARG*/ // Inputs a, b) input a; `ifdef SUB_IS_A_FOOBAR `define SUB_CELL foobar `else `define SUB_CELL foobiz `endif `SUB_CELL subcell (/*AUTOINST*/);For this to work, you need to read the defines with the below at the bottom of your file Verilogmode will use the last definition of SUB_CELL to determine which one to pickup the pinlist from

System Verilog Macro A Powerful Feature For Design Verification Projects

Verilog Tutorial 13 Define Parameter And Localparam Youtube

Macros can be used to improve the readability and maintainability of the Verilog code `ifdef, `ifndef, `elsif, `else and `endif conditionally compiles Verilog code, depending on whether or not a specified macro is defined Any code that is not compiled must still be valid Verilog code `include includes the contents of another Verilog source fileThis page contains Verilog tutorial, Verilog Syntax, Verilog Quick Reference, PLI, modelling memory and FSM, `ifdef Optionally includes lines of source code during compilation The `ifdef directive checks that a macro has been defined, and if so, compiles the code that follows If the macro has not been defined, the compiler compiles theIn this Verilog tutorial, we demonstrate usage of Verilog `define text macros, and `ifdef compiler directiveComplete example from the Verilog tutorial http

Quick Reference Verilog Hdl

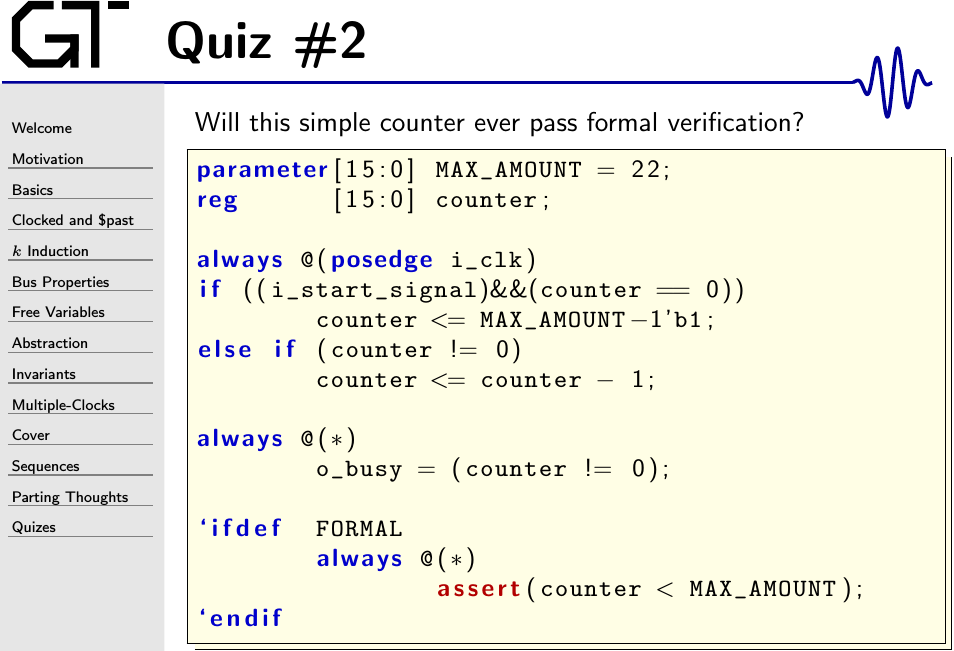

Quiz 2 Will This Counter Pass Formal Verification

Verilog has very simple data types and it's all defined by Verilog language (users cannot define their own data types in Verilog) Verilog has two main data types including net data types (for connecting components together such as wire (most popular), wor, wand, tri, trior, etc ) and variable data types (for temporary storage such as regUsing the GUI to define the 'ifdef doesn't help I have verilog like 'ifdef PARAM_1 INST_ASIC_MEM_1 'elsif INST_ASIC_MEM_2 'else INST_FPGA_MEM In this case I want the 'else to be executed I have set the PARAM_1 & PARAM_2 to ZERO from the project settings, as suggested on this discussion FYI I am using 134 VivadoVerilog `ifdef `elsif Example The following example has two display statements inside separate `ifdef scopes which does not have a default `else part to it So this means that by default nothing will be displayed If the macro either MACRO is defined, the corresponding display message is included and will be displayed during simulation

Ovl Usage Guidelines Eda Stds Org Home Page Pages 1 8 Flip Pdf Download Fliphtml5

Mac S Emacs Mode

The `define compiler directive is used to perform global macro substitution and remain active for all files read/compiled after the macro definition It will available until another macro definition changes the value or until the macro is undefined using the `undef compiler directive `define WIDTH 8 to avoid redefincation `ifdef can be used`ifdef, `else, and `endif These directives can be used to decide which lines of Verilog code should be included for the compilation (Example 4) The `ifdef directive checks if a macro name that follows this directive is defined If it is, then all lines between `ifdef and `else will be includedThis answer is not useful Show activity on this post #if defined (CONDITION1) defined (CONDITION2) should work ) #ifdef is a bit less typing, but

Digital System Design Verilog Hdl Parameters And Generate

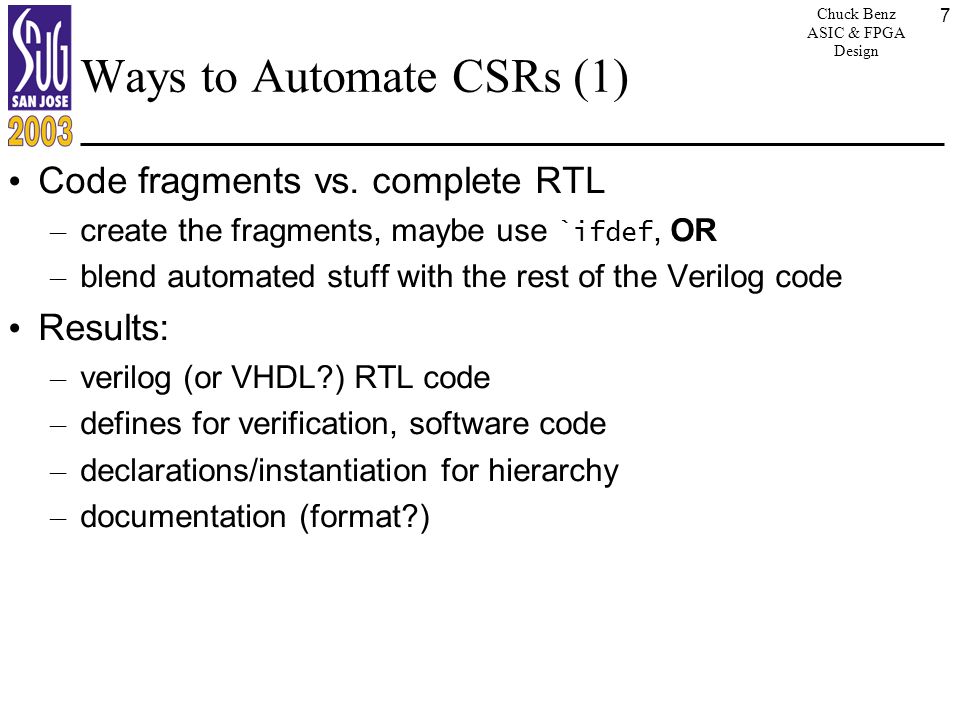

Chuck Benz Asic Fpga Design Csrgen Automated Csrs For Asic Fpga Processor Interfaces Chuck Benz Chuck Benz Asic Fpga Design Ppt Download

`endif We manually put in the ifdef, as we would have if not using Verilogmode Verilogmode a signal referenced before the AUTOARG, leaves that text alone, and omits that signal in its output Why not automatic?The #ifdef, #ifndef , #elseif, #elif, #else, and

0 件のコメント:

コメントを投稿